-

read more »

read more »ATOM one

ATOM one is the smallest Full HD camera with Dual 3G-SDI output.

The camera is based on Sony’s IMX174 image sensor that provides exceptional image performance with multi matrix support. -

read more »

read more »ASIC, FPGA and SoC development

System on Chip (SoC), FPGA and embedded software designs for consumer electronics, telecommunications and automotive industries

-

weiterlesen »

weiterlesen »ASIC, FPGA und SoC Entwicklung

Ihr deutsches Systemhaus für die Chip und FPGA Entwicklung im deutschspraching Raum. Embedded Software Entwicklung und Leiterkartenentwicklung auf höchstem Niveau.

-

read more »

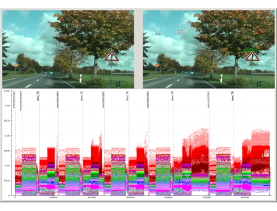

read more »Cutting-edge Image Processing for ADAS

Experience the future of driving with our state-of-the-art components for automotive safety!

-

weiterlesen »

weiterlesen »Bildverarbeitung für Fahrerassistenzsysteme

Algorithmen und Komponenten für das autonome Fahren. Embedded Software Entwicklung nach ISO 26262. Autosar Entwicklung auf Infineon Aurix Bausteinen.

-

read more »

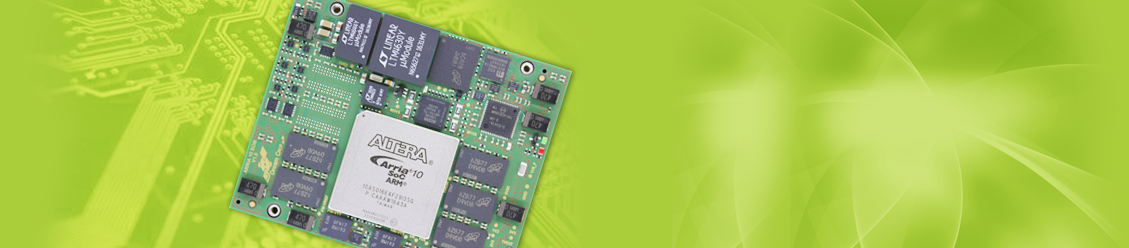

read more »Arria 10 System on Module

The Arria 10 SOM is an Arria 10 SoC System on Module with an emphasis on embedded and automotive vision applications. Using Alteras Arria 10 SoC Devices in the 29x29 mm package, the module off ers a multitude of interfaces in a small 10 cm by 6 cm form factor.

FPGA emulation methodology for fast and accurate power estimation of embedded processors

This work presents an FPGA accelerated power estimation methodology for programmable processors based on a hybrid functional level (FLPA) and instruction level power analysis (ILPA) that can be mapped onto an FPGA together with the functional emulation. It enables fast and accurate estimation of application-specific power consumption and energy per task which is crucial for power-aware design of embedded processor architectures. The approach allows both hardware and software designers to optimize their implementations not only for processing performance but also for power efficiency. The power emulation methodology and considerations for the FPGA implementation of the power estimation is described in detail. Model validation against GTL power simulation and results are given for a typical embedded RISC processor and a commercial-grade Application Specific Instruction Set Processor (ASIP). Power consumption models yield fast and accurate power estimation with a %MAE of less than 9% and NRMSE of less than 7% enabling co-optimization of both hardware and software with respect to power consumption in early design stages.

Please download the full article from here.